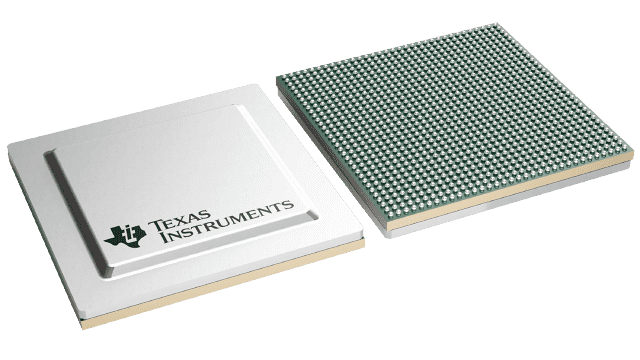

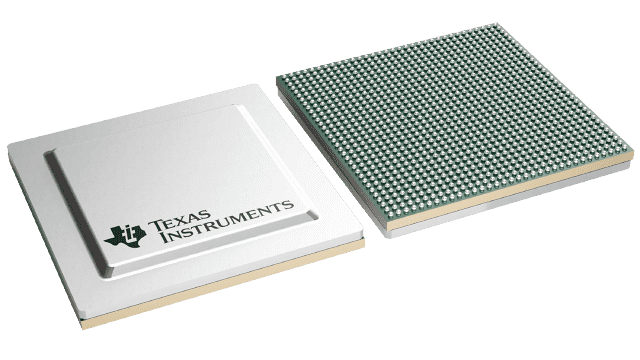

66AK2E05XABD25

ActiveHIGH PERFORMANCE MULTICORE DSP+ARM - 4X ARM A15 CORES, 1X C66X DSP CORE, NETCP, 10GBE

Deep-Dive with AI

Search across all available documentation for this part.

66AK2E05XABD25

ActiveHIGH PERFORMANCE MULTICORE DSP+ARM - 4X ARM A15 CORES, 1X C66X DSP CORE, NETCP, 10GBE

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

| Specification | 66AK2E05XABD25 |

|---|---|

| Clock Rate | 1.25 GHz |

| Interface | MDIO, DMA, I2C, USIM, USB 3.0, EBI/EMI, TSIP, Ethernet, SPI, PCIe, UART/USART |

| Mounting Type | Surface Mount |

| Non-Volatile Memory | 256 kB |

| On-Chip RAM | 2 MB |

| Operating Temperature [Max] | 85 °C |

| Operating Temperature [Min] | 0 °C |

| Package / Case | 1089-BFBGA, FCBGA |

| Supplier Device Package | 1089-FCBGA (27x27) |

| Type | DSP+ARM® |

| Voltage - Core | Variable |

| Voltage - I/O | 1.5 V, 1.35 V, 3.3 V, 1.8 V |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

| Digikey | Tray | 40 | $ 160.86 | |

| Texas Instruments | JEDEC TRAY (5+1) | 1 | $ 138.91 | |

| 100 | $ 125.74 | |||

| 250 | $ 122.14 | |||

| 1000 | $ 119.75 | |||

Description

General part information

66AK2E05 Series

The 66AK2E0x is a high performance device based on TI’s KeyStone II Multicore SoC Architecture, incorporating the most performance-optimized Cortex-A15 processor single-core or quad-core CorePac and C66x DSP core, that can run at a core speed of up to 1.4 GHz. TI’s 66AK2E0x device enables a high performance, power-efficient and easy to use platform for developers of a broad range of applications such as enterprise grade networking end equipment, data center networking, avionics and defense, medical imaging, test and automation.

TI’s KeyStone II Architecture provides a programmable platform integrating various subsystems (for example, ARM CorePac (Cortex-A15 Processor Quad Core CorePac), C66x CorePac, network processing, and uses a queue-based communication system that allows the device resources to operate efficiently and seamlessly. This unique device architecture also includes a TeraNet switch that enables the wide mix of system elements, from programmable cores to high-speed IO, to each operate at maximum efficiency with no blocking or stalling.

TI’s C66x core launches a new era of DSP technology by combining fixed-point and floating point computational capability in the processor without sacrificing speed, size, or power consumption. The raw computational performance is an industry-leading 38.4 GMACS/core and 19.2 Gflops/core (@ 1.2 GHz operating frequency). It can execute 8 single precision floating point MAC operations per cycle and can perform double- and mixed-precision operations and is IEEE754 compliant. For fixed-point use, the C66x core has 4× the multiply accumulate (MAC) capability of C64×+ cores. The C66x CorePac incorporates 90 new instructions targeted for floating point and vector math oriented processing. These enhancements yield sizeable performance improvements in popular DSP kernels used in signal processing, mathematical, and image acquisition functions. The C66x core is backwards code compatible with TI'’s previous generation C6000 fixed and floating point DSP cores, ensuring software portability and shortened software development cycles for applications migrating to faster hardware.

Documents

Technical documentation and resources