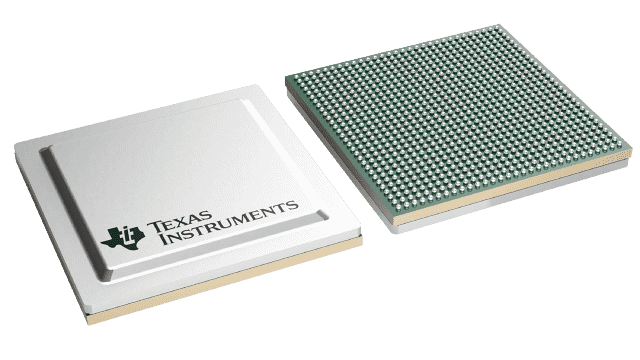

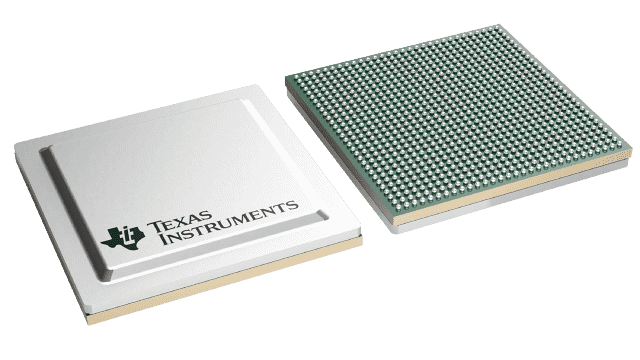

66AK2L06XCMS2

ActiveMULTICORE DSP+ARM KEYSTONE II SYSTEM-ON-CHIP (SOC)

Deep-Dive with AI

Search across all available documentation for this part.

66AK2L06XCMS2

ActiveMULTICORE DSP+ARM KEYSTONE II SYSTEM-ON-CHIP (SOC)

Technical Specifications

Parameters and characteristics for this part

| Specification | 66AK2L06XCMS2 |

|---|---|

| Clock Rate | 1.2 GHz |

| Interface | DMA, UART/USART, Ethernet, USB 3.0, USIM, SPI, I2C, PCIe, EBI/EMI |

| Mounting Type | Surface Mount |

| Non-Volatile Memory | 384 kB |

| On-Chip RAM | 5.384 MB |

| Operating Temperature [Max] | 100 °C |

| Operating Temperature [Min] | 0 °C |

| Package / Case | 900-BFBGA, FCBGA |

| Supplier Device Package | 900-FCBGA (25x25) |

| Type | DSP+ARM® |

| Voltage - Core | Variable |

| Voltage - I/O | 3.3 V, 1 V, 1.8 V, 0.85 V |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

| Digikey | Tray | 44 | $ 584.72 | |

| Texas Instruments | JEDEC TRAY (5+1) | 1 | $ 524.65 | |

| 100 | $ 474.90 | |||

| 250 | $ 461.33 | |||

| 1000 | $ 452.29 | |||

Description

General part information

66AK2L06 Series

The 66AK2L06 KeyStone SoC is a member of the C66x family based on TI's new KeyStone II Multicore SoC Architecture and is a low-power solution with integrated JESD204B lanes that meets the more stringent power, size, and cost requirements of applications requiring connectivity with ADC and DAC based applications. The device’s ARM and DSP cores deliver exceptional processing power on platforms requiring high signal and control processing.

TI’s KeyStone II Architecture provides a programmable platform integrating various subsystems (ARM CorePac, C66x CorePacs, IP network, Digital Front End, and FFT processing) and uses a queue-based communication system that allows the SoC resources to operate efficiently and seamlessly. This unique SoC architecture also includes a TeraNet switch that enables the wide mix of system elements, from programmable cores to dedicated coprocessors and high-speed IO, to each operate at maximum efficiency with no blocking or stalling.

The addition of the ARM CorePac in the 66AK2L06 device enables the ability for complex control code processing on-chip. Operations such as housekeeping and management processing can be performed with the Cortex-A15 processor.

Documents

Technical documentation and resources