XIO2221ZAY

ObsoletePCI EXPRESS™ TO 1394B OHCI WITH 1-PORT PHY

Deep-Dive with AI

Search across all available documentation for this part.

XIO2221ZAY

ObsoletePCI EXPRESS™ TO 1394B OHCI WITH 1-PORT PHY

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

| Specification | XIO2221ZAY |

|---|---|

| Applications | PCI Express to PCI Translation Bridge |

| Interface | IEEE 1394 |

| Mounting Type | Surface Mount |

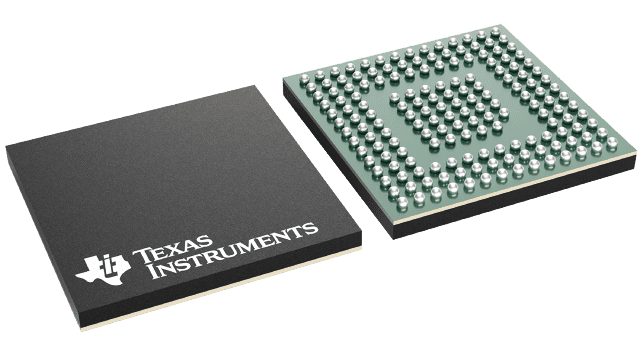

| Package / Case | 167-LFBGA |

| Supplier Device Package | 167-NFBGA (12x12) |

| Voltage - Supply [Max] | 3.6 V, 1.65 V |

| Voltage - Supply [Min] | 1.35 V, 3 V |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

| Texas Instruments | JEDEC TRAY (5+1) | 1 | $ 10.63 | |

| 100 | $ 9.28 | |||

| 250 | $ 7.16 | |||

| 1000 | $ 6.40 | |||

Description

General part information

XIO2221 Series

The TI XIO2221 is a PCIe to PCI translation bridge, where the PCI bus interface is internally connected to a 1394b open host controller/link-layer controller with a 1-port 1394b PHY. The PCIe to PCI translation bridge is fully compatible with the PCI Express to PCI/PCI-X Bridge Specification, Revision 1.0. Also, the bridge supports the standard PCI-to-PCI bridge programming model. The 1394b OHCI controller function is fully compatible with IEEE Std 1394b and the latest 1394 Open Host Controller Interface (OHCI) Specification.

The XIO2221 simultaneously supports up to four posted write transactions, four nonposted transactions, and four completion transactions pending in each direction at any time. Each posted write data queue and completion data queue can store up to 8K bytes of data. The nonposted data queues can store up to 128 bytes of data.

The PCIe interface supports a ×1 link operating at full 250 Mbit/s packet throughput in each direction simultaneously. Also, the bridge supports the advanced error reporting capability including ECRC as defined in the PCI Express Base Specification, Revision 1.1. Supplemental firmware or software is required to fully utilize both of these features.

Documents

Technical documentation and resources