DAC8221GP

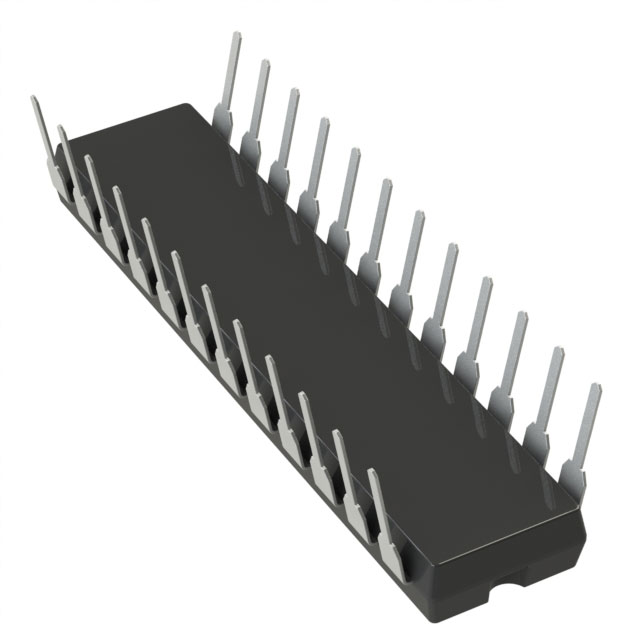

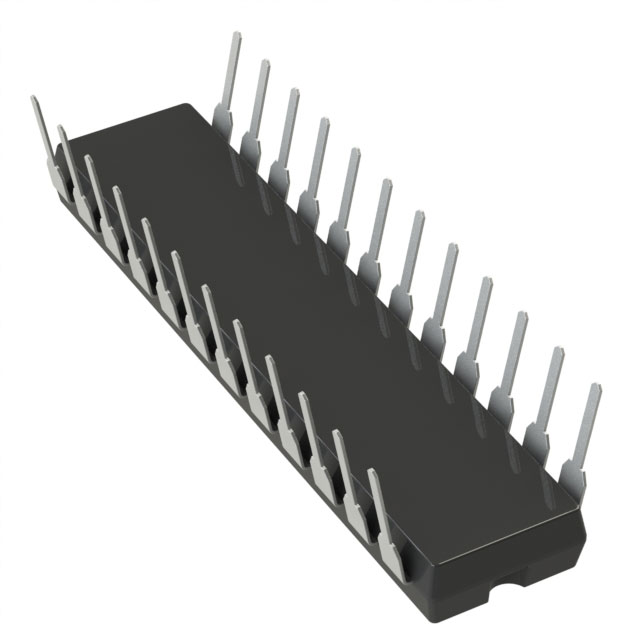

ObsoleteIC DAC 12BIT A-OUT 24DIP

Deep-Dive with AI

Search across all available documentation for this part.

DAC8221GP

ObsoleteIC DAC 12BIT A-OUT 24DIP

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

| Specification | DAC8221GP |

|---|---|

| Architecture | R-2R |

| Data Interface | Parallel |

| Differential Output | False |

| INL/DNL (LSB) | 0.2 LSB, 0.2 LSB |

| Mounting Type | Through Hole |

| Number of Bits | 12 bits |

| Operating Temperature [Max] | 70 °C |

| Operating Temperature [Min] | 0 °C |

| Output Type | Current - Unbuffered |

| Package / Case | 0.3 in |

| Package / Case | 24-DIP |

| Package / Case | 7.62 mm |

| Reference Type | External |

| Settling Time | 1 µs |

| Supplier Device Package | 24-PDIP |

| Voltage - Supply, Analog [Max] | 15 V |

| Voltage - Supply, Analog [Min] | 5 V |

| Voltage - Supply, Digital [Max] | 15 V |

| Voltage - Supply, Digital [Min] | 5 V |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

Description

General part information

5962-8967101 Series

The DAC-8221 combines two identical 12-bit, multiplying, digital-to-analog converters into a single CMOS chip. This device is electrically similar to DAC-8212 with improved microprocessor interface timing and is packaged in a narrow 0.300" DIP. Monolithic construction offers excellent DAC-to-DAC matching and tracking over the full operating temperature range. The DAC-8221 consists of two thin-film R-2R resistor-ladder networks, two 12-bit data latches, one 12-bit input buffer, and control logic. The DAC-8221 operates on a single supply from +5V to +15V. Maximum power dissipation with 0V and +5V logic levels and a +5V supply is less than 0.5mW. The DAC-8221 is manufactured using PMI's highly-stable, thin film resistors on an advanced oxide-isolated, silicon-gate, CMOS process. PMI's improved latch-up resistant design eliminates the need for external protective Schottky diodes.A common 12-bit (TTL/CMOS compatible) input port is used to load a 12-bit-wide word into either of the two DACs. This port, whose data loading is similar to that of a RAM's write cycle, interfaces directly with most 12-bit or wider bus systems. WithWRandCSlines at logic LOW, the input data registers are transparent. This allows direct unbuffered data to flow directly to the DAC output selected byDAC A/DAC B control input.

Documents

Technical documentation and resources